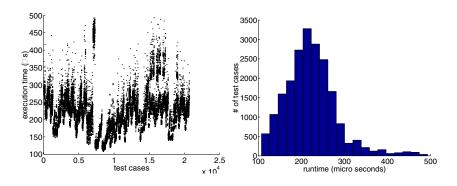

# Lecture Notes in Computer Science

Edited by G. Goos, J. Hartmanis, and J. van Leeuwen

2017

# Springer Berlin

Berlin

Heidelberg

New York

Barcelona

Hong Kong

London

Milan

Paris

Tokyo

Samuel P. Midkiff José E. Moreira Manish Gupta Siddhartha Chatterjee Jeanne Ferrante Jan Prins William Pugh Chau-Wen Tseng (Eds.)

# Languages and Compilers for Parallel Computing

13th International Workshop, LCPC 2000 Yorktown Heights, NY, USA, August 10-12, 2000 Revised Papers

#### Volume Editors

Samuel P. Midkiff

José E. Moreira

Manish Gupta

Siddhartha Chatterjee

IBM T.J. Watson Research Center

P.O. Box 218, Yorktown Heights, NY 10598, USA E-mail: {smidkiff,jmoreira,mgupta,sc}@us.ibm.com

Jeanne Ferrante

University of California at San Diego, Computer Science and Engineering

9500 Gilman Drive, La Jolla, CA 92093-0114, USA

E-mail: ferrante@cs.ucsd.edu

Jan Prins

University of North Carolina, Department of Computer Science

Chapel Hill, NC 27599-3175, USA

E-mail: prins@unc.edu

William Pugh

Chau-Wen Tseng

University of Maryland, Department of Computer Science

College Park, MD 20742, USA

E-mail: {pugh,tseng}@cs.umd.edu

Cataloging-in-Publication Data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Languages and compilers for parallel computing: 13th international workshop; revised papers / LCPC 2000, Yorktown Heights, NY, USA, August 10 - 12, 2000.

Samuel P. Midkiff ... (ed.). - Berlin; Heidelberg; New York; Barcelona;

Hong Kong; London; Milan; Paris; Tokyo: Springer, 2002

(Lecture notes in computer science; Vol. 2017)

ISBN 3-540-42862-3

CR Subject Classification (1998): D.3, D.1.3, F.1.2, B.2.1, C.2

ISSN 0302-9743

ISBN 3-540-42862-3 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2001 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Boller Mediendesign Printed on acid-free paper SPIN: 10782214 06/3142 5 4 3 2 1 0

#### Foreword

This volume contains the papers presented at the 13th International Workshop on Languages and Compilers for Parallel Computing. It also contains extended abstracts of submissions that were accepted as posters. The workshop was held at the IBM T. J. Watson Research Center in Yorktown Heights, New York. As in previous years, the workshop focused on issues in optimizing compilers, languages, and software environments for high performance computing. This continues a trend in which languages, compilers, and software environments for high performance computing, and not strictly parallel computing, has been the organizing topic. As in past years, participants came from Asia, North America, and Europe.

This workshop reflected the work of many people. In particular, the members of the steering committee, David Padua, Alex Nicolau, Utpal Banerjee, and David Gelernter, have been instrumental in maintaining the focus and quality of the workshop since it was first held in 1988 in Urbana-Champaign. The assistance of the other members of the program committee – Larry Carter, Sid Chatterjee, Jeanne Ferrante, Jans Prins, Bill Pugh, and Chau-wen Tseng – was crucial. The infrastructure at the IBM T. J. Watson Research Center provided trouble-free logistical support. The IBM T. J. Watson Research Center also provided financial support by underwriting much of the expense of the workshop. Appreciation must also be extended to Marc Snir and Pratap Pattnaik of the IBM T. J. Watson Research Center for their support.

Finally, we would like to thank the referees who spent countless hours assisting the program committee members in evaluating the quality of the submissions: Scott B. Baden, Jean-Francois Collard, Val Donaldson, Rudolf Eigenmann, Stephen Fink, Kang Su Gatlin, Michael Hind, Francois Irigoin, Pramod G. Joisha, Gabriele Keller, Wolf Pfannenstiel, Lawrence Rauchweger, Martin Simons, D. B. Skillicorn, Hong Tang, and Hao Yu.

January 2001

Manish Gupta Sam Midkiff José Moreira

# Organization

The 13th annual International Workshop on Languages and Compilers for High Performance Computing (LCPC 2000) was organized and sponsored by the IBM T. J Watson Research Center, Yorktown Heights, New York

#### Steering Committee

Utpal Banerjee Intel Corporation

David Gelernter Yale University

Alex Nicolau University of California at Irvine

David A. Padua University of Illinois at Urbana-Champaign

#### **Program Committee**

Jans Prins University of North Carolina at Chapel Hill

Bill Pugh University of Maryland Chau-Wen Tseng University of Maryland

## **Sponsoring Institutions**

The IBM T. J. Watson Research Center, Yorktown Heights, New York

# **Table of Contents**

| Presented Pa | pers |

|--------------|------|

|--------------|------|

| Accurate Shape Analysis for Recursive Data Structures                                                                                                                                 | 1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Cost Hierarchies for Abstract Parallel Machines                                                                                                                                       | 6 |

| Recursion Unrolling for Divide and Conquer Programs                                                                                                                                   | 4 |

| An Empirical Study of Selective Optimization                                                                                                                                          | 9 |

| MaJIC: A Matlab Just-In-time Compiler                                                                                                                                                 | 8 |

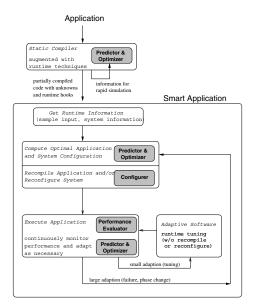

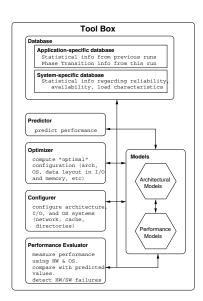

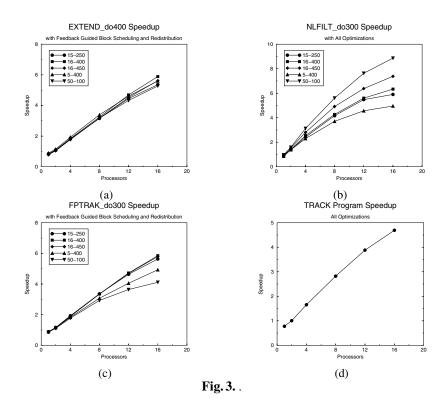

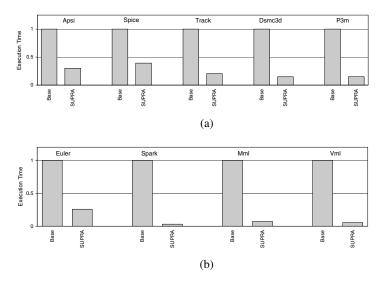

| SmartApps: An Application Centric Approach to High Performance                                                                                                                        |   |

| Computing                                                                                                                                                                             | 2 |

| Extending Scalar Optimizations for Arrays                                                                                                                                             | 7 |

| Searching for the Best FFT Formulas with the SPL Compiler                                                                                                                             | 2 |

| On Materializations of Array-Valued Temporaries                                                                                                                                       | 7 |

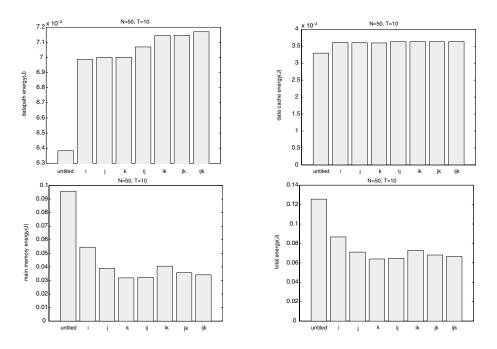

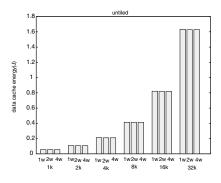

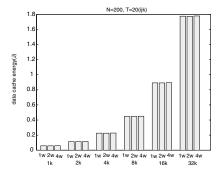

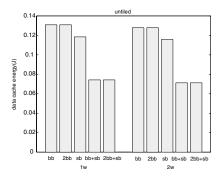

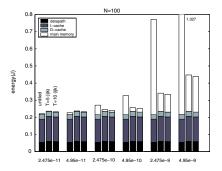

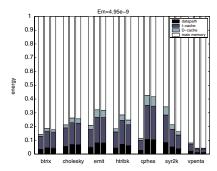

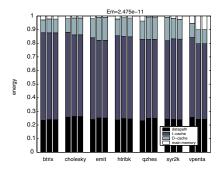

| Experimental Evaluation of Energy Behavior of Iteration Space Tiling 14  Mahmut Kandemir, Narayanan Vijaykrishnan, Mary Jane Irwin, and  Hyun Suk Kim (Pennsylvania State University) | 2 |

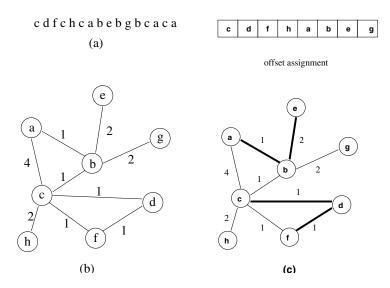

| Improving Offset Assignment for Embedded Processors                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

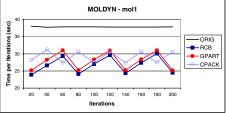

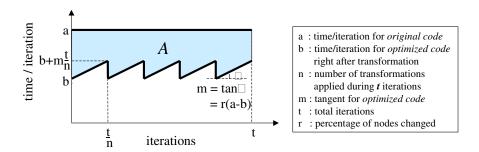

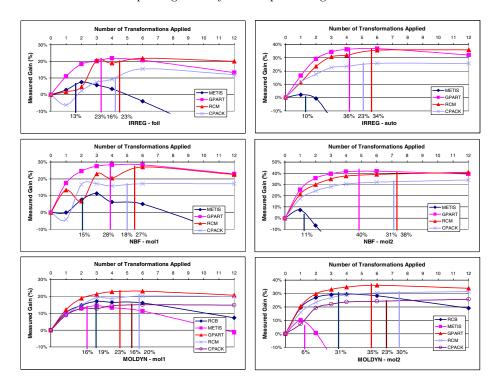

| Improving Locality for Adaptive Irregular Scientific Codes                                                                                                                                              |

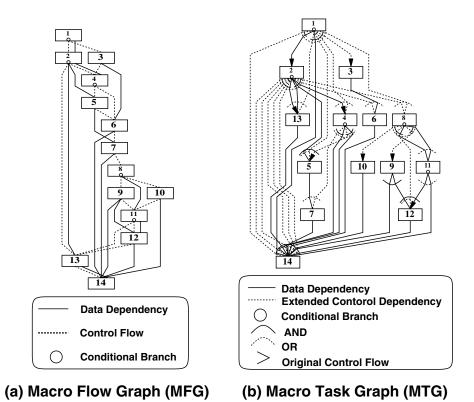

| Automatic Coarse Grain Task Parallel Processing on SMP Using OpenMP                                                                                                                                     |

| Compiler Synthesis of Task Graphs for Parallel Program Performance Prediction                                                                                                                           |

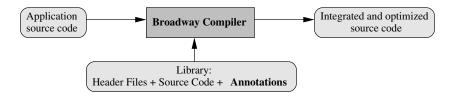

| Optimizing the Use of High Performance Software Libraries                                                                                                                                               |

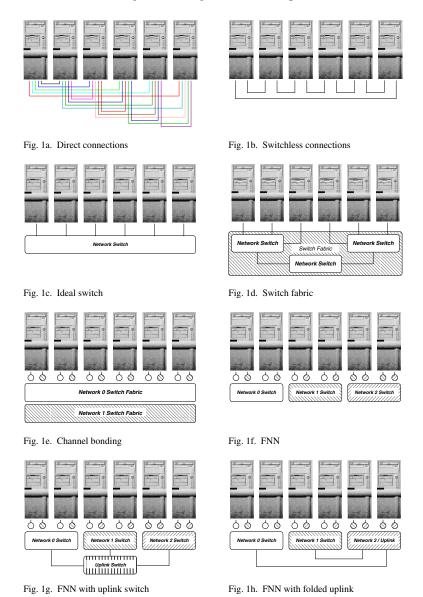

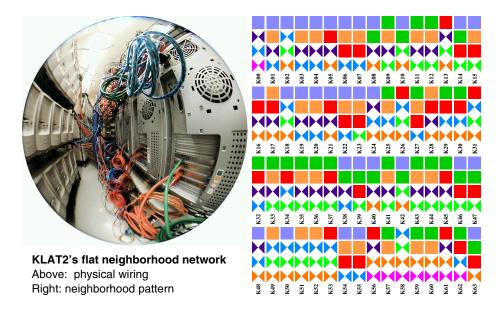

| Compiler Techniques for Flat Neighborhood Networks                                                                                                                                                      |

| Exploiting Ownership Sets in HPF                                                                                                                                                                        |

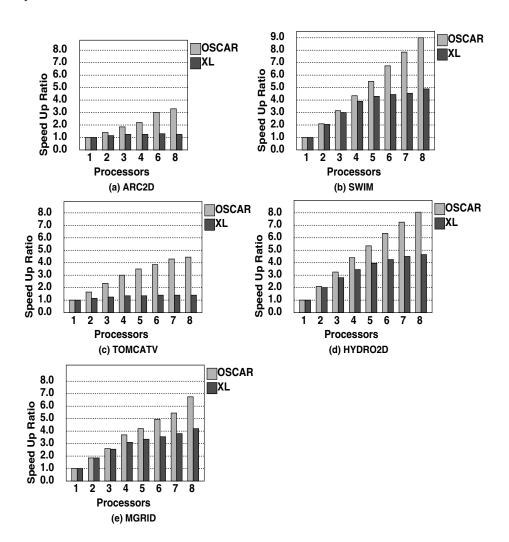

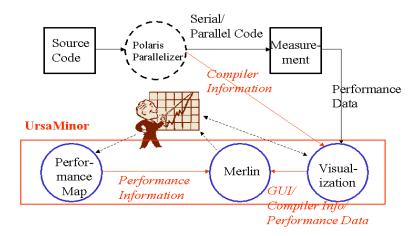

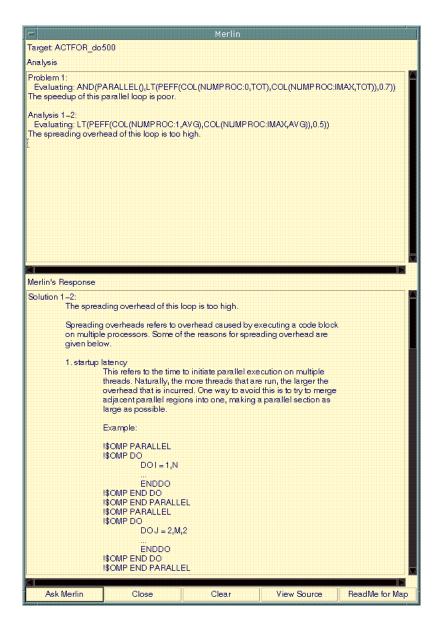

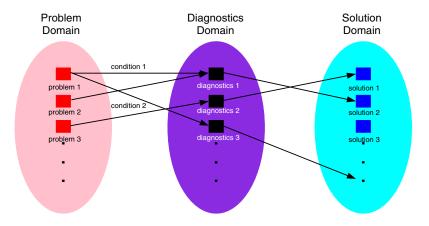

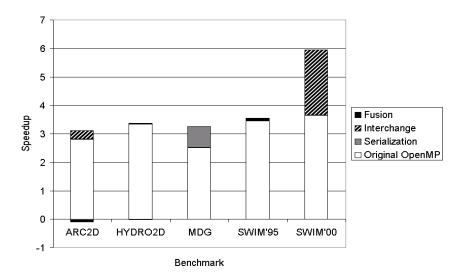

| A Performance Advisor Tool for Shared-Memory Parallel Programming 274<br>Seon Wook Kim, Insung Park, and Rudolf Eigenmann (Purdue<br>University)                                                        |

| A Comparative Analysis of Dependence Testing Mechanisms                                                                                                                                                 |

| Safe Approximation of Data Dependencies in Pointer-Based Structures 304 D.K. Arvind and T.A. Lewis (The University of Edinburgh)                                                                        |

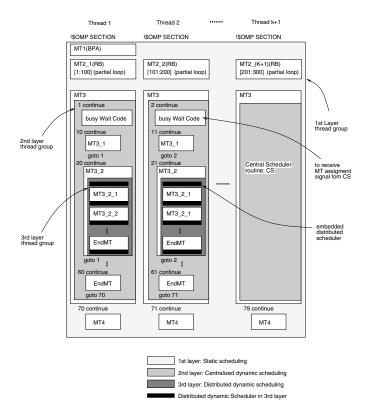

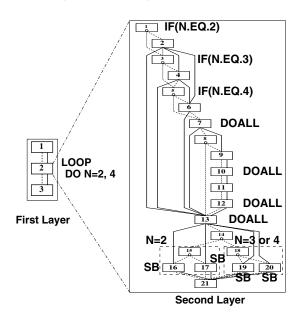

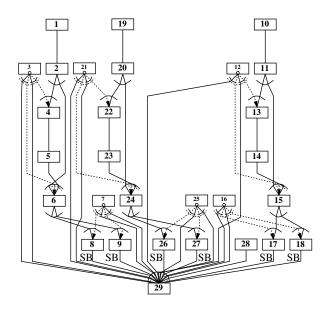

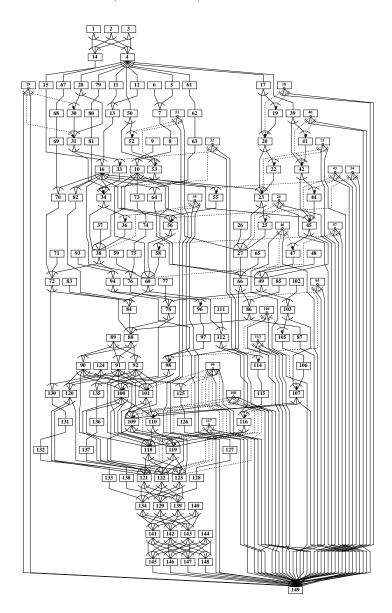

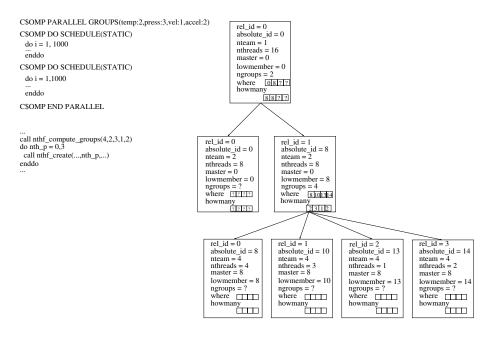

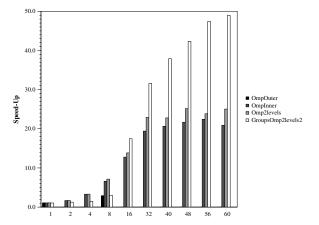

| OpenMP Extensions for Thread Groups and Their Run-Time Support 324  Marc Gonzalez, Jose Oliver, Xavier Martorell, Eduard Ayguade,  Jesus Labarta, and Nacho Navarro (Technical University of Catalonia) |

| Compiling Data Intensive Applications with Spatial Coordinates                                                                                                                                          |

| $\mathbf{P}$ | OS | st. | 61 | ·s |

|--------------|----|-----|----|----|

| 1            | w  | 7 L | CI |    |

| Efficient Dynamic Local Enumeration for HPF                |

|------------------------------------------------------------|

| Issues of the Automatic Generation of HPF Loop Programs    |

| Run-Time Fusion of MPI Calls in a Parallel C++ Library     |

| Set Operations for Orthogonal Processor Groups             |

| Compiler Based Scheduling of Java Mobile Agents            |

| A Bytecode Optimizer to Engineer Bytecodes for Performance |

| Author Index                                               |

# Accurate Shape Analysis for Recursive Data Structures\*

Francisco Corbera, Rafael Asenjo, and Emilio Zapata

Dept. Computer Architecture, University of Málaga, Spain {corbera,asenjo,ezapata}@ac.uma.es

Abstract. Automatic parallelization of codes which use dynamic data structures is still a challenge. One of the first steps in such parallelization is the automatic detection of the dynamic data structure used in the code. In this paper we describe the framework and the compiler we have implemented to capture complex data structures generated, traversed, and modified in C codes. Our method assigns a Reduced Set of Reference Shape Graphs (RSRSG) to each sentence to approximate the shape of the data structure after the execution of such a sentence. With the properties and operations that define the behavior of our RSRSG, the method can accurately detect complex recursive data structures such as a doubly linked list of pointers to trees where the leaves point to additional lists. Other experiments are carried out with real codes to validate the capabilities of our compiler.

#### 1 Introduction

For complex and time-consuming applications, parallel programming is a must. Automatic parallelizing compilers are designed with the aim of dramatically reducing the time needed to develop a parallel program by generating a parallel version from a sequential code without special annotations. There are several well-known research groups involved in the development and improvement of parallel compilers, such as Polaris, PFA, Parafrase, SUIF, etc. We have noted that the detection step of current parallelizing compilers does a pretty good job when dealing with regular or numeric codes. However, they cannot manage irregular codes or symbolic ones, which are mainly based on complex data structures which use pointers in many cases. Actually, data dependence analysis is quite well known for array-based codes even when complex array access functions are present [5]. On the other hand, much less work has been done to successfully determine the data dependencies of code sections using dynamic data structures based on pointers. Nevertheless, this is a problem that cannot be avoided due to the increasing use of dynamic structures and memory pointer references.

$<sup>^\</sup>star$  This work was supported by the Ministry of Education and Science (CICYT) of Spain (TIC96-1125-C03), by the European Union (BRITE-EURAM III BE95-1564), by APART: Automatic Performance Analysis: Resources and Tools, EU Esprit IV Working Group No. 29488

With this motivation, our goal is to propose and implement new techniques that can be included in compilers to allow the automatic parallelization of real codes based on dynamic data structures. From this goal we have selected the shape analysis subproblem, which aims at estimating at compile time the shape the data will take at run time. Given this information, a subsequent analysis would detect whether or not certain sections of the code can be parallelized because they access independent data regions.

There are several ways this problem can be approached, but we focus in the graph-based methods in which the "storage chunks" are represented by nodes, and edges are used to represent references between them [2], [8], [9]. In a previous work [3], we combined and extended several ideas from these previous graph-based methods, for example, allowing more than a summary node per graph among other extensions. However, we keep the restriction of one graph per sentence in the code. This way, since each sentence of the code can be reached after following several paths in the control flow, the associated graph should approximate all the possible memory configurations arising after the execution of this sentence. This restriction leads to memory and time saving, but at the same time it significantly reduces the accuracy of the method. In this work, we have changed our previous direction by selecting a tradeoff solution: we consider several graphs with more than a summary node, while fulfilling some rules to avoid an explosion in the number of graphs and nodes in each graph.

Among the first relevant studies which allowed several graphs were those developed by Jones et al. [7] and Horwitz et al. [6]. These approaches are based on a "k-limited" approximation in which all nodes beyond a k selectors path are joined in a summary node. The main drawback to these methods is that the node analysis beyond the "k-limit" is very inexact and therefore they are unable to capture complex data structures. A more recent work that also allows several graphs and summary nodes is the one presented by Sagiv et al. [10]. They propose a parametric framework based on a 3-valued logic. To describe the memory configuration they use 3-valued structures defined by several predicates. These predicates determine the accuracy of the method. As far as we know the currently proposed predicates do not suffice to deal with the complex data structures that we handle in this paper.

With this in mind, our proposal is based on approximating all the possible memory configurations that can arise after the execution of a sentence by a set of graphs: the *Reduced Set of Reference Shape Graphs* (RSRSG). We see that each RSRSG is a collection of *Reference Shape Graphs* (RSG) each one containing several non-compatible nodes. Finally, each node represents one or several memory locations. Compatible nodes are "summarized" into a single one. Two nodes are compatible if they share the same reference properties. With this framework we can achieve accurate results without excessive compilation time. Besides this, we cover situations that were previously unsolved, such as detection of complex structures (lists of trees, lists of lists, etc.) and structure permutation, as we will see in this article.

The rest of the paper is organized as follows. Section 2 briefly describes the whole framework, introducing the key ideas of the method and presenting the data structure example that will help in understanding node properties and operations with graphs. These properties are described in Sect. 3 where we show how the RSG can accurately approximate a memory configuration. The analysis method have been implemented in a compiler which is experimentally validated, in Sect. 4, by analyzing several C codes based on complex data structures. Finally, we summarize the main contributions and future work in Sect. 5.

#### 2 Method Overview

Basically, our method is based on approximating all possible memory configurations that can appear after the execution of a sentence in the code. Note that due to the control flow of the program, a sentence could be reached by following several paths in the control flow. Each "control path" has an associated memory configuration which is modified by each sentence in the path. Therefore, a single sentence in the code modifies all the memory configurations associated with all the control paths reaching this sentence. Each memory configuration is approximated by a graph we call *Reference Shape Graphs* (RSG). So, taking all this into account, we conclude that each sentence in the code will have a set of RSGs associated with it. This set of RSGs will describe the shape of the data structure after the execution of this sentence.

The calculation of this set of graphs is carried out by the **symbolic execution** of the program over the graphs. In this way, each program sentence transforms the graphs to reflect the changes in the memory configurations derived from the sentence execution. The RSGs are graphs in which nodes represent memory locations which have similar reference patterns. Therefore, a single node can safely and accurately represents several memory locations (if they are similarly referenced) without losing their essential characteristics.

To determine whether or not two memory locations should be represented by a single node, each one is annotated with a set of properties. Now, two different memory locations will be "summarized" in a single node if they fulfill the same properties. Note that the node inherits the properties of the memory locations represented by this node. Besides this, two nodes can be also summarized if they represent "summarizable" memory locations. This way, a possibly unlimited memory configuration can be represented by a limited size RSG, because the number of different nodes is limited by the number of properties of each node. These properties are related to the reference pattern used to access the memory locations represented by the node. Hence the name Reference Shape Graph.

As we have said, all possible memory configurations which may arise after the execution of a sentence are approximated by a set of RSGs. We call this set *Reduced Set of Reference Shape Graphs* (RSRSG), since not all the different RSGs arising in each sentence will be kept. On the contrary, several RSGs related to different memory configurations will be fused when they represent memory locations with similar reference patterns. There are also several properties related to the RSGs, and two RSGs should share these properties to be joined. Therefore, besides the number of nodes in an RSG, the number of different RSGs associated with a sentence are limited too. This union of RSGs greatly reduces the number of RSGs and leads to a practicable analysis.

The symbolic execution of the code consists in the abstract interpretation of each sentence in the code. This abstract interpretation is carried out iteratively for each sentence until we reach a fixed point in which the resulting RSRSG associated with the sentence does not change any more [4]. This way, for each sentence that modifies dynamic structures, we have to define the abstract semantics which describes how these sentences modify the RSRSG. We consider six simple instructions that deal with pointers: x = NULL, x = malloc, x = y,  $x \to sel = NULL$ ,  $x \to sel = y$ , and  $x = y \to sel$ . More complex pointer instructions can be built upon these simple ones and temporal variables.

The output RSRSG resulting from the abstract interpretation of a sentence over an input  $RSRSG_i$  is generated by applying the abstract interpretation to each  $rsg_i \in RSRSG_i$ . After the abstract interpretation of the sentence over the  $rsg_i \in RSRSG_i$  we obtain a set of output  $rsg_o$ . As we said, we cannot keep all the  $rsq_0$  arising from the abstract interpretation. On the contrary, each  $rsg_o$  will be compressed, which means the summarization of compatible nodes in the  $rsg_o$ . Furthermore, some of the  $rsg_o$ s can be fused in a single RSG if they represent similar memory configurations. This operation greatly reduces the number of RSGs in the resulting RSRSG. In the worst case, the sequence of operations that the compiler carries out in order to symbolically execute a sentence are: graph division, graph prune, sentence symbolic execution (RSG modification), RSG compression and RSG union to build the final RSRSG. Due to space constraints we cannot formally describe this operations neither the abstract semantics carried out by the compiler. However, in order to provide an overview of our method we present a data structure example which will be referred to during the framework and operations description.

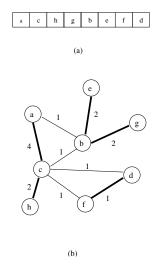

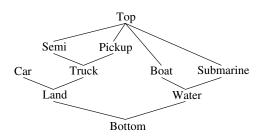

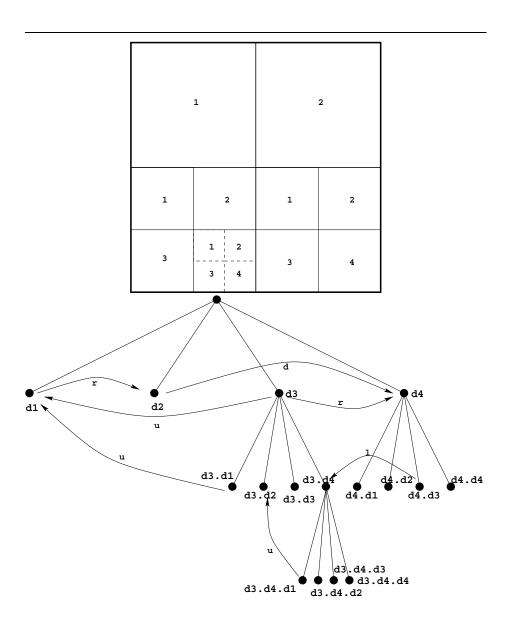

#### 2.1 Working Example

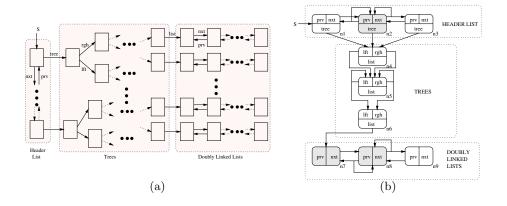

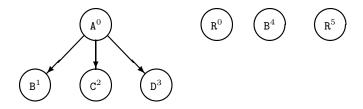

The data structure, presented in Fig. 1 (a), is a doubly linked list of pointers to trees. Besides this, the leaves of the trees have pointers to doubly linked lists. The pointer variable S points to the first element of the doubly linked list (header list). Each item in this list has three pointers: nxt, prv, and tree. This tree selector points to the root of a binary tree in which each element has the lft and rgh selectors. Finally, the leaves of the trees point to additional doubly linked lists. All the trees pointed to by the header list are independent and do not share any element. In the same way, the lists pointed to by the leaves of the same tree or different trees are also independent.

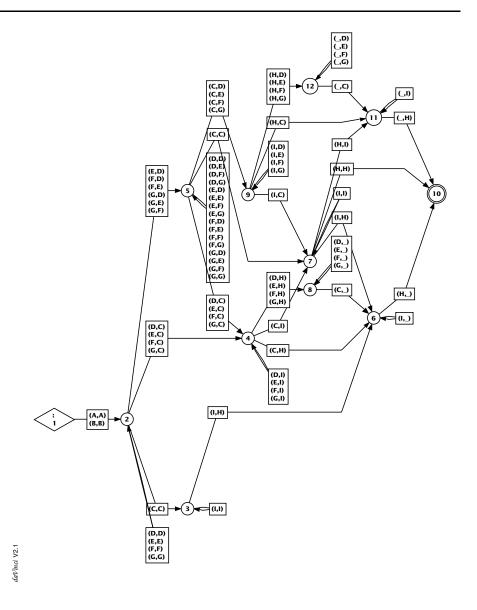

This data structure is built by a C code which traverses the elements of the header list with two pointers and eventually can permute two trees. Our compiler has analyzed this code obtaining an RSRSG for each sentence in the program. Figure 1 (b) shows a compact representation of the RSRSG obtained for the last sentence of the code after the compiler analysis.

Fig. 1. A complex data structure and compact representation of the resulting RSRSG.

As we will see in the next sections, from the RSRSG represented in Fig. 1 (b) we can infer the actual properties of the real data structure: the trees and lists do not share elements and therefore they can be traversed in parallel. These results and other examples of real codes (sparse matrix-vector multiplication, sparse LU factorization and Barnes-Hut N-body simulation) with different data structures are presented in Sect. 4. But first, we describe our framework with a formal description of the RSGs in the next section.

### 3 Reference Shape Graph

First, we need to present the notation used to describe the different memory configurations that may arise when executing a program.

**Definition 1** We call a collection of dynamic structures a memory configuration. These structures comprise several memory chunks, that we call memory locations, which are linked by references. Inside these memory locations there is room for data and for pointers to other memory locations. These pointers are called selectors.

We represent the memory configurations with the tuple M = (L, P, S, PS, LS) where:  $\mathbf{L}$  is the set of memory locations;  $\mathbf{P}$  is the set of pointer variables (pvars) used in the program;  $\mathbf{S}$  is the set of selectors declared in the data structures;  $\mathbf{PS}$  is the set of references from pvars to memory locations, of the type < pvar, l >, with pvar  $\in P$  and  $l \in L$ ; and  $\mathbf{LS}$  is the set of links between memory locations, of the form  $< l_1, sel, l_2 >$  where  $l_1 \in L$  references  $l_2 \in L$  by selector  $sel \in S$ .

We will use L(m), P(m), S(m), PS(m), and LS(m) to refer to each one of these sets for a particular memory configuration, m.

Therefore, we can assume that the RSRSG of a program sentence is an approximation of the memory configuration, M, after the execution of this sen-

tence. But let us first describe the RSGs now that we know how a memory configuration is defined.

**Definition 2** An RSG is a graph represented by the tuple RSG = (N, P, S, PL, NL) where:  $\mathbf{N}$ : is the set of nodes. Each node can represent several memory locations if they fulfill certain common properties;  $\mathbf{P}$ : is the set of pointer variables (pvars) used in the program;  $\mathbf{S}$ : is the set of declared selectors;  $\mathbf{PL}$ : is the set of references from pvars to nodes, of the type < pvar, n > with pvar  $\in P$  and  $n \in N$ ; and  $\mathbf{NL}$ : is the set of links between nodes, of the type <  $n_1$ , sel,  $n_2 >$  where  $n_1 \in N$  references  $n_2 \in N$  by selector sel  $\in S$ .

We will use N(rsg), P(rsg), S(rsg), PL(rsg), and NL(rsg) to refer to each one of these sets for a particular RSG, rsg.

To obtain the RSG which approximates the memory configuration, M, an abstraction function is used,  $F:M\to RSG$ . This function maps memory locations into nodes and references to memory locations into references to nodes at the same time. In other words, F, translates the memory domain into the graph domain. This, function F comprises three functions:  $F_n:L\to N$  takes care of mapping memory locations into nodes;  $F_p:PS\to PL$  maps references from powers to memory locations into references from powers to nodes, and  $F_l:LS\to NL$  maps links between locations into links between nodes.

It is easy to see that:  $F_p(< pvar, l >) = < pvar, n > \text{iif } F_n(l) = n \text{ and } F_l(< l_1, sel, l_2 >) = < n_1, sel, n_2 > \text{iif } F_n(l_1) = n_1 \wedge F_n(l_2) = n_2 \text{ which means that translating references to locations into references to nodes is trivial after mapping locations into nodes. This translates almost all the complexity involved in function <math>F$  to function  $F_n$  which actually maps locations into nodes.

Now we focus on  $F_n$  which extracts some important properties from a memory location and, depending on these, this location is translated into a node. Besides this, if several memory locations share the same properties then this function maps all of them into the same node of the RSG. Due to this dependence on the location properties, the  $F_n$  function will be described during the presentation of the different *properties* which characterize each node. These properties are: Type, Structure, Simple Paths, Reference pattern, Share information, and Cycle links. These are now described.

#### 3.1 Type

This property tries to extract information from the code text. The idea is that two pointers of different types should not point to the same memory location (for example, a pointer to a graph and another to a list). Also, the memory location pointed to by a graph pointer should be considered as a graph. This way, we assign the TYPE property, of a memory location l, from the type of the pointer variable used when that memory location l is created (by malloc or in the declarative section of the code).

Therefore, two memory locations,  $l_1$  and  $l_2$ , can be mapped into the same node if they share the same TYPE value: If  $F_n(l_1) = F_n(l_2) = n$  then TYPE $(l_1) = r$

TYPE( $l_2$ ), where the TYPE() function returns the TYPE value. Note that we can use the same property name and function, TYPE(), for both memory locations and nodes. Clearly, TYPE(n) = TYPE(l) when  $F_n(l) = n$ .

This property leads to the situation where, for the data structure presented in Fig. 1 (a), the nodes representing list memory locations will not be summarized with those nodes representing tree locations, as we can see in Fig. 1 (b).

#### 3.2 Structure

As we have just seen, the TYPE property keeps two different nodes for two memory locations of different types. However, we also want to avoid the summarization of two nodes which represent memory locations of the same type but which do not share any element. That is, they are non-connected components. This behavior is achieved by the use of the STRUCTURE property, which takes the same value for all memory locations (and nodes) belonging to the same connected component. Again, two memory locations can be represented by the same node if they have the same STRUCTURE value: If  $F_n(l_a) = F_n(l_b) = n$  then STRUCTURE( $l_a$ ) = STRUCTURE( $l_a$ )

This leads to the condition that two locations must fulfill in order to share the same STRUCTURE value: STRUCTURE  $(l_a) = \text{STRUCTURE}(l_b) = val \text{ iif } \exists l_1, ..., l_i | (< l_a, sel_1, l_1 >, < l_1, sel_2, l_2 >, ..., < l_i, sel_{i+1}, l_b > \in LS) \lor (< l_b, sel_1, l_1 >, < l_1, sel_2, l_2 >, ..., < l_i, sel_{i+1}, l_a > \in LS), \text{ which means that two memory locations, } l_a \text{ and } l_b, \text{ have the same STRUCTURE value if there is a path from } l_a \text{ to } l_b \text{ (first part of the previous equation) or from } l_b \text{ to } l_a \text{ (second part of the equation)}.$  In the same way we can define STRUCTURE(n).

#### 3.3 Simple Paths

The SPATH property further restricts the summarizing of nodes. Simple paths denominates the access path from a pointer variable (pvar) to a location or node. An example of a simple path is  $p \to s$  in which the pvar p points to the location s. In this example the simple path for s is . The use of the simple path avoids the summarization of nodes which are directly pointed to by the pvars (actually, these nodes are the entry points to the data structure). We define the SPATH property for a memory location  $l \in L(m)$  as SPATH(l) =  $\{p_1, ..., p_n\}$  where  $< p_i, l > \in PS(m)$ . This property is similarly defined for the RSG domain. Now, two memory locations are represented by the same node if they have the same SPATH (If  $F_n(l_1) = F_n(l_2)$  then SPATH( $l_1$ ) = SPATH( $l_2$ ).

#### 3.4 Reference Patterns

This new property is introduced to classify and represent by different nodes the memory locations with different reference patterns. We understand by reference pattern the type of selectors which point to a certain memory location and which point from this memory location to others.

This is particularly useful for keeping singular memory locations of the data structure in separate nodes. For example, the head/tail and the rest of the elements of a single linked list are two kinds of memory locations. These will be represented by different nodes, because the head location is not referenced by other list entries and the tail location does not reference any other list location. The same would also happen for more complex data structures built upon more simple structures (such as lists of lists, trees of lists, etc.). For example, in Fig. 1 (a), the root of one of the trees is referenced by the header list and the leaves do not point to tree items but to a doubly linked list. Thanks to the reference patterns, the method results in the RSRSG of Fig. 1 (b), where the root of the tree, the leaves, and the other tree items are clearly identified.

In order to obtain this behavior, we define two sets SELINset and SELOUTset which contain the set of input and output selectors for a location:  $\mathtt{SELINset}(l_1) = \{sel_i \in S | \exists l_2 \in L, < l_2, sel_i, l_1 > \in LS\}$  and  $\mathtt{SELOUTset}(l_1) = \{sel_i \in S | \exists l_2 \in L, < l_1, sel_i, l_2 > \in LS\}$ , where we see that  $sel_i$  is in the  $\mathtt{SELINset}(l_1)$  if  $l_1$  is referenced from somewhere by selector  $sel_i$ , or  $sel_i$  is in  $\mathtt{SELOUTset}(l_1)$  if  $l_1.sel_i$  points to somewhere outside.

#### 3.5 Share Information

This is a key property for informing the compiler about the potential parallelism exhibited by the analyzed data structure. Actually, the share information can tell whether at least one of the locations represented by a node is referenced more than once from other memory locations. That is, a shared node represents memory locations which can be accessed from several places and this may prevent the parallelization of the code section which traverses these memory locations. From another point of view, this property helps us to determine if a cycle in the RSG graph is representing cycles in the data structure approximated by this RSG or not.

Due to the relevance of this property, we use two kinds of attributes for each node: (i) SHARED(n) with  $n \in N(rsg)$ , is a Boolean function which returns "true" if any of the locations,  $l_1$ , represented by n are referenced by other locations,  $l_2$ and  $l_3$ , by different selectors,  $sel_i$  and  $sel_j$ . Therefore, this SHARED function tells us whether there may be a cycle in the data structure represented by the RSG or not. If SHARED(n) is 0, we know that even if we reach the node n by  $sel_1$  and later by  $sel_2$ , we are actually reaching two different memory locations represented by the same n node, and therefore there is no cycle in the approximated data structure. (ii) SHSEL(n, sel) with  $n \in N(rsg)$  and  $sel \in S$ , is a Boolean function which returns "true" if any of the memory locations,  $l_1$ , represented by n can be referenced more than once by selector sel from other locations,  $l_2$  and  $l_3$ . This way, with the SHSEL function, we can distinguish two different situations that can be represented by an RSG with a node, n, and a selector, sel, pointing to itself. If SHSEL(n, sel) = 0 we know that this node is representing an acyclic unbounded data structure (the size is not known at compile time). For example, in a list, all the elements of the list (locations) are represented by the same node, n, but following selector sel we always reach a different memory location. On the other hand, if SHSEL(n, sel) = 1, for the same list example, by following selector sel we can reach an already visited location, which means that there are cycles in the data structure.

Let's illustrate these SHARED and SHSEL properties using the compact representation of the RSRSG presented in Fig. 1 (b). In this Fig., shaded nodes have the SHARED property set to true. For example, in the header list the middle node  $n_2$  is shared, SHARED $(n_2)=1$ , because  $n_2$  is referenced by selectors nxt and prv. However, the SHSEL $(n_2, nxt)=$ SHSEL $(n_2, prv)=0$  which means that by following selector nxt or prv it is not possible to reach an already visited memory location. Actually, in this example, there are no selectors with the SHSEL property set to true. So, the same happens for node  $n_8$  which represents the middle items of the doubly linked lists.

We can also see in Fig. 1 (b), that node  $n_4$  is not shared, which states that, in fact, from memory locations represented by  $n_1$ ,  $n_2$ , and  $n_3$  we can reach different trees which do not share any elements (as we see in Fig. 1 (a)). Finally, node  $n_7$  is shared because it is pointed to by selectors *list* and *prv*. However, due to SHSEL $(n_7, list)=0$  we can ensure that two different leaves of the trees will never point to the same doubly linked list.

#### 3.6 Cycle Links

The goal of this property is to increase the accuracy of the data structure representation by avoiding unnecessary edges that can appear during the RSG updating process.

The cycle links of a node, n, are defined as the set of pairs of references  $\langle sel_i, sel_j \rangle$  such that when starting at node n and consecutively following selectors  $sel_i$  and  $sel_j$ , the n node is reached again. More precisely, for  $n \in N(rsg)$  we define:  $\texttt{CYCLELINKS}(n) = \{\langle sel_i, sel_j \rangle | sel_i, sel_j \in S\}$ , such that if  $\langle sel_i, sel_j \rangle \in \texttt{CYCLELINKS}(n)$  then:  $\forall l_i, F_n(l_i) = n$ , if  $\langle l_i, sel_i, l_j \rangle \in LS$  then  $\exists \langle l_i, sel_i, l_i \rangle \in LS$ .

This CYCLELINKS set maintains similar information to that of "identity paths" in the Abstract Storage Graph (ASG) [8], which is very useful for dealing with doubly-linked structures. For example, in the data structure presented in Fig. 1 (a), the elements in the middle of the doubly linked lists have two cycle links:  $\langle nxt, prv \rangle$  and  $\langle prv, nxt \rangle$ , due to starting at a list item and consecutively following selectors nxt and prv (or prv and nxt) the starting item is reached. Note, that this does not apply to the first or last element of the doubly linked list. This property is captured in the RSRSG shown in Fig. 1 (b) where we see three nodes for the double linked lists (one for the first element of the list, another for the last element, and another between them to represent the middle items in the list). This middle node,  $n_8$ , is annotated by our compiler with CYCLELINKS( $n_8$ ) = { $\langle nxt, prv \rangle$ ,  $\langle prv, nxt \rangle$ }.

We conclude here that the CYCLELINKS property is used during the pruning process which take place after the node materialization and RSG modification. So, in contrast with the other five properties described in previous subsections,

the CYCLELINKS property does not prevent the summarization of two nodes with do not share the CYCLELINKS sets and therefore do not affect the  $F_n$  function.

#### 3.7 Compression of Graphs

After the symbolic execution of a sentence over an input RSRSG, the resulting RSRSG may contain RSGs with redundant information, which can be removed due to node summarization or compression of the RSG.

In order to do this, after the symbolic execution of a sentence, the method applies the COMPRESS function over the just modified RSGs. This COMPRESS function first call to the boolean C\_NODES\_RSG one, which identifies the compatible nodes that will later be summarized. This Boolean function just has to check whether or not the first five properties previously described are the same for both nodes (as we said in the previous subsection the CYCLELINKS property does not affect the compatibility of two nodes).

There is a similar function which returns true when two memory locations are compatible. With this, we can finally define  $F_n$  as the function which maps all the compatible memory locations into the same node, which happens when they have the same TYPE, STRUCTURE, SPATH and SHARED properties, and compatible reference patterns.

#### 4 Experimental Results

All the previously mentioned operations and properties have been implemented in a compiler written in C which analyzes a C code to generate the RSRSG associated with each sentence of the code. As we said, the symbolic execution of each sentence over an RSRSG is going to generate a modified RSRSG. Before the symbolic execution of the code, the compiler can also extract some important information from the program in a previous pass. For example, a quite frequent pattern arising in C codes based on dynamic data structures is the following: while (x != NULL) { ... }.

In this case the compiler can assert that at the entry of the while body the pvar  $x \neq NULL$ . Besides this, if we have not exited the while body with a break sentence, we can also ensure that just after the while body the pvar x = NULL. This information is used to simplify the analysis and increase the accuracy of the method. More precisely, we can reduce the number of RSGs and/or reduce the complexity of this RSG by diminishing the number of memory configurations represented by each RSG. Other sentences from which we can extract useful information are IF-THEN-ELSE, FOR loops, or any conditional sentence.

The implementation of this idea has been carried out by the definition of certain pseudoinstructions that we call FORCE. These pseudoinstructions are inserted in the code by the first pass of the compiler and will be symbolically executed as regular sentences. Therefore, each one of these FORCE sentences has its own abstract semantics and its own associated RSRSG. The FORCE pseudoinstructions we have considered are:  $\text{FORCE}_{[x==NULL]}(rsg)$ ,  $\text{FORCE}_{[x!=NULL]}(rsg)$ ,  $\text{FORCE}_{[x==y]}(rsg)$ ,  $\text{FORCE}_{[x]=y]}(rsg)$ ,  $\text{FORCE}_{[x]=sel=NULL]}(rsg)$ .

In addition, we have found that the FORCE<sub>[x!=NULL]</sub> pseudoperation can be also placed just before the following sentences:  $x \to sel = NULL$ ,  $x \to sel = y$ ,  $y = x \to sel$  and for any sentence with an occurrence of the type  $x \to val$ , where val is a non-pointer field, under the assumption that the code is correct. That is, it makes sense to assume that before the execution of all these three sentences, x is not NULL (in other cases the code would produce an error at execution time).

With the compiler described we have analyzed the code which generates, traverses, and modifies several codes: the working example presented in section 2.1, the Sparse Matrix-vector multiplication, the Sparse LU factorization and the Barnes-Hut code. All these codes were analyzed by our compiler in a Pentium III 500MHz with 128MBytes main memory. The time and memory required by the compiler are summarized in table 1. The particular aspects of these codes are described next.

**Table 1.** Time and space required by the compiler to analyze several codes

|       | Working Example | S. Matrix-vector | S. LU factorization | Barnes-Hut |

|-------|-----------------|------------------|---------------------|------------|

| Time  | 0'13"           | 0'04"            | 1'38"               | 4'04"      |

| Space | 2.7 MB          | 1.6 MB           | 24 MB               | 47 MB      |

#### 4.1 Working Example's RSRSG

We refer in this subsection to the code that generates, traverses, and modifies the data structure presented in Fig. 1 (a). A compact representation of the resulting RSRSG for the last sentence of the code can be seen in Fig. 1 (b). Although we do not show the code due to space constraints, we have to say that this code presents an additional difficulty due to some tree permutations being carried out during data structure modification. The problem arising during structure permutation is that it is very easy to temporally assign the SHARED=true property to the root of one of the trees that we are permutating, when this root is temporally pointed to by two different locations from the header list. If this shared property remains true after the permutation we would have a shaded  $n_4$  node in Fig. 1 (b). This would imply that two different items from the header list can point to the same tree (which would prevent the parallel execution of traversing the trees). However, this problem is solved because, after the permutation, the method reassigns false to the shared property thanks to the combination of our properties and the division of graph operations. Summarizing, after the compiler analyzes this code, the compact representation of the resulting RSRSG for the last sentence of the program (Fig. 1 (b)) accurately describes the data structure depicted in Fig. 1 (a) in the sense that: (i) The compiler successfully detects the doubly linked list which is acyclic by selectors nxt or prv and whose elements point to binary trees; (ii) As  $SHSEL(n_4, tree) = 0$ , we can say that two different items of the header list cannot point to the same tree; (iii) At the same time, as no tree node  $(n_4, n_5 \text{ and } n_6)$  is shared, we can say that different trees do not share items; (iv) The same happens for the doubly linked list pointed to by the tree leaves: all the lists are independent, there are no two leaves pointing to the same list, and these lists are acyclic by selectors nxt or prv.

Besides this, our compiler has also analyzed three C program kernels which generate, traverse, and modify complex dynamic data structures which we describe next.

#### 4.2 Sparse Matrix-Vector Multiplication

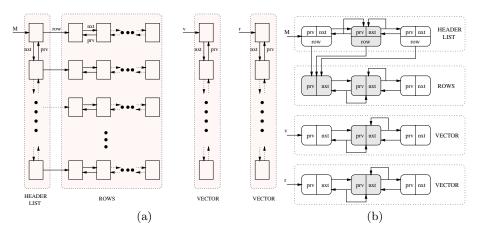

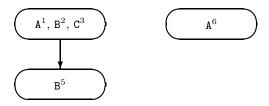

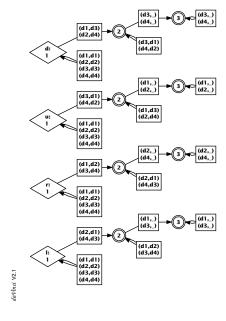

Here we deal with an irregular code which implements a sparse matrix by vector multiplication,  $r=M\times v$ . The sparse matrix, M, is stored in memory as a header doubly linked list with pointers to other doubly linked lists which store the matrix rows. The sparse vectors, v and r are also doubly linked lists. This can be seen in Fig. 2(a). Note that vector r grows during the multiplication process.

Fig. 2. Sparse matrix-vector multiplication data structure and compacted RSRSG.

After the analysis process, carried out by our compiler, the resulting RSRSG accurately represents this data structure. Actually, in Fig. 2(b) we present a compact representation of the resulting RSRSG for the last sentence of the code. First, note that the three structures involved in this code are kept in separate subgraphs. Even when the data type for vectors v and r and rows of M, is the same, the STRUCTURE property avoids the union of these graphs into a single one. This RSRSG states that the rows of the matrix are pointed to from different elements of the header list (there is no selector with the shared property set to true). Also, the doubly linked lists which store the rows of M and the vectors v and r are acyclic by selectors nxt and prv.

The same RSRSG is also reached just before the execution of the outermost loop which takes care of the matrix multiplication, but without the r subgraph which is generated during this multiplication.

#### 4.3 Sparse LU Factorization

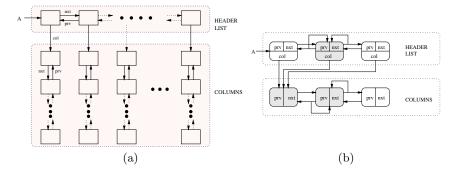

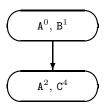

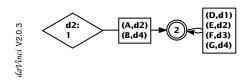

The kernel of many computer-assisted scientific applications is to solve large sparse linear systems. The code we analyze now solves non-symmetric sparse linear systems by applying the LU factorization of the sparse matrix, computed by using a general method. In particular, we have implemented an in-place code for the direct right-looking LU algorithm, where an n-by-n matrix A is factorized. The code includes a column pivoting operation (partial pivoting) to provide numerical stability and preserve sparseness. The input matrix A columns as well as the resulting in place LU columns are stored in one-dimensional doubly linked lists (see Fig. 3 (a)), to facilitate the insertion of new entries and to allow column permutations.

Fig. 3. Sparse LU factorization data structure and compacted RSRSG.

After the LU code analysis we obtain the same RSRSG for the sentences just after the matrix initialization and after the LU factorization. A compact representation of this RSRSG is shown in Fig. 3(b). As we can see, variable A points to a doubly linked list, the header list and each node of this list points to a single doubly linked list which represents a matrix column. The properties of the data structure represented by this RSRSG can be inferred following the same arguments we presented in the previous subsection.

#### 4.4 Barnes-Hut N-body Simulation

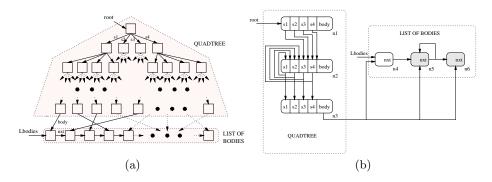

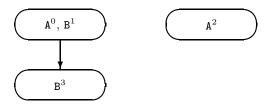

This code is based on the algorithm presented in [1] which is used in astrophysics. The data structure used in this code is based on a hierarchical octree representation of space in three dimensions. In two dimensions, a quadtree representation is used. However, due to memory constraints (the octree and the quadtree versions run out of memory in our 128MB Pentium III) we have simplified the code to use a binary tree. In Fig. 4(a) we present a schematic view of the data structure used in this code. The bodies are stored by a single linked list pointed to by the pvar *Lbodies*.

Fig. 4. Barnes-Hut data structure and compacted RSRSG.

After the code analysis, the compact representation of the RSRSG at the end of each step of the algorithm is presented in Fig. 4(b). We can see that the root of the tree is represented by node  $n_1$ , the middle elements of the tree by node  $n_2$  and the leaves by  $n_3$ . Note that these leaves can point to any body stored in the *Lbodies* list represented by nodes  $n_4$ ,  $n_5$ , and  $n_6$ . As tree nodes are not shared and selectors also have the SHSEL property set to false, a subsequent analysis of the code can state that the tree can be traversed and updated in parallel. This analysis can also conclude that there are no two different leaves pointing to the same body (entry in the *Lbodies* list) due to nodes  $n_4$ ,  $n_5$ , and  $n_6$  not being shared by selector body.

#### 5 Conclusions and Future Work

We have developed a compiler which can analyze a C code to determine the RSRSG associated with each sentence of the code. Each RSRSG contains several RSGs, each one representing the different data structures which may arise after following different paths in the control flow graph of the code. However, several RSGs can be joined if they represent similar data structures, in this way reducing the number of RSGs associated with a sentence. Every RSG contains nodes which represent one or several memory locations. To avoid an explosion in the number of nodes, all the memory locations which are similarly referenced are represented by the same node. This reference similarity is captured by the properties we assign to the memory locations. In comparison with previous works, we have increased the number of properties assigned to each node. This leads to more nodes in the RSG because the nodes now have to fulfill more properties to be summarized. However, by avoiding the summarization of these nodes, we keep a more accurate representation of the data structure. This is a key issue when analyzing the parallelism exhibited by a code.

Our compiler symbolically executes each sentence in the code, transforming the RSGs to reflect the modifications in the data structure that are carried out due to the execution of the sentence. We have validated the compiler with several C codes which generate, traverse, and modify complex dynamic data structures, such as a doubly linked list of pointers to trees where the leaves point to other doubly linked lists. Other structures have been also accurately identified by the compiler, even in the presence of structure permutations (for example, column permutations in the sparse LU code). As far as we know, there is no compiler achieving such successful results for these kinds of data structures appearing in real codes.

In the near future we will develop an additional compiler pass that will automatically analyze the RSRSGs and the code to determine the parallel loops of the program and allow the automatic generation of parallel code.

#### References

- J. Barnes and P. Hut. A Hierarchical O(n· log n) force calculation algorithm. Nature v.324, December 1986.

- D. Chase, M. Wegman and F. Zadeck. Analysis of Pointers and Structures. In SIGPLAN Conference on Programming Language Design and Implementation, 296-310. ACM Press, New York, 1990.

- F. Corbera, R. Asenjo and E.L. Zapata New shape analysis for automatic parallelization of C codes. In ACM International Conference on Supercomputing, 220– 227, Rhodes, Greece, June 1999.

- P. Cousot and R. Cousot. Abstract interpretation: A unified lattice model for static analysis of programs by construction of approximation of fixed points. In Proceedings of the ACM Symposium on Principles of Programming Languages. ACM Press, New York. 238–252, 1977.

- J. Hoeflinger and Y. Paek The Access Region Test. In Twelfth International Workshop on Languages and Compilers for Parallel Computing (LCPC'99), The University of California, San Diego, La Jolla, CA USA, August, 1999.

- S. Horwitz, P. Pfeiffer, and T. Reps. Dependence Analysis for Pointer Variables. In Proceedings of the SIGPLAN Conference on Programming Language Design and Implementation, 28-40, June 1989.

- N. Jones and S. Muchnick. Flow Analysis and Optimization of Lisp-like Structures. In Program Flow Analysis: Theory and Applications, S. Muchnick and N. Jones, Englewood Cliffs, NJ: Prentice Hall, Chapter 4, 102-131, 1981.

- J. Plevyak, A. Chien and V. Karamcheti. Analysis of Dynamic Structures for Efficient Parallel Execution. In Languages and Compilers for Parallel Computing, U. Banerjee, D. Gelernter, A. Nicolau and D. Padua, Eds. Lectures Notes in Computer Science, vol 768, 37-57. Berlin Heidelberg New York: Springer-Verlag 1993.

- M. Sagiv, T. Reps and R. Wilhelm. Solving Shape-Analysis problems in Languages with destructive updating. ACM Transactions on Programming Languages and Systems, 20(1):1-50, January 1998.

- M. Sagiv, T. Reps, and R. Wilhelm, Parametric shape analysis via 3-valued logic. In Conference Record of the Twenty-Sixth ACM Symposium on Principles of Programming Languages, San Antonio, TX, Jan. 20-22, ACM, New York, NY, 1999, pp. 105-118.

#### Cost Hierarchies for Abstract Parallel Machines

John O'Donnell<sup>1</sup>, Thomas Rauber<sup>2</sup>, and Gudula Rünger<sup>3</sup>

<sup>1</sup> Computing Science Department, University of Glasgow, Glasgow G12 8QQ, Great Britain jtod@dcs.gla.ac.uk

Institut für Informatik, Universität Halle-Wittenberg, 06099 Halle(Saale), Germany rauber@informatik.uni--halle.de

<sup>3</sup> Fakultät für Informatik, Technische Universität Chemnitz, 09107 Chemnitz, Germany ruenger@informatik.tu-chemnitz.de

Abstract. The Abstract Parallel Machine (APM) model separates the definitions of parallel operations from the application algorithm, which defines the sequence of parallel operations to be executed. An APM contains a set of parallel operation definitions, which specify how the computation is organized into independent sites of computation and what data exchanges are required. This paper adds explicit cost models as the third component of an APM system. The costs of parallel operations can be obtained either by analyzing a parallel operation definition, or by measuring performance on a real machine. Costs with monotonicity constraints allow the cost of an algorithm to be transformed automatically as the algorithm itself is transformed.

#### 1 Introduction

There is increasing recognition of the fundamental role that cost models play in the design of parallel programs [19]. They enable the time and space complexity of a program to be determined, as for sequential algorithms, but parallel cost models serve several additional purposes. For example, intuition is often an inadequate basis for making the right choices about organizing the parallelism and using the system's resources. Suitable high level cost models allow the programmer to assess each alternative quantitatively during the design process, improving efficiency without requiring an inordinate amount of programming time. Portability of the efficiency is one of the chief problems in parallel programming, and cost models can help here by indicating where an algorithm should be modified to make effective use of a particular machine's capabilities. Such motivations have led to a plethora of approaches to cost modeling.

APMs (abstract parallel machines [14, 15]) are an approach for describing parallel programming models, especially in the context of program transformation. In this approach the parallel behavior is encapsulated in a set of ParOps (parallel operations), which are analogous to combinators in data parallel programming [13] and skeletons in BMF [5, 4]. An explicit separation is made between the definitions of the ParOps and the specific parallel algorithm to be

implemented. An APM consists of a set of ParOps and a coordination language; algorithms are built up from the ParOps of one APM and are expressed using a coordination language for that APM. APMs are not meant as programming languages; rather, they illustrate programming models and their relationships, and provide a basis for algorithm transformation. The relationships between different parallel operations can be clarified with a hierarchy of related APMs.

There is some notion of costs already inherent in the definition of an APM, since the parallel operation definitions state how the operation is organized into parallel sites and what communications are required. The cost of an algorithm is determined by the costs of the ParOps it uses, and the cost of a ParOp could be derived from its internal description. This would allow a derivation to be based only on the information inside the APM definition. However, this is not the only way to obtain costs, and a more general and explicit treatment of costs can be useful.

In this paper, we enrich the APM approach by adding an explicit hierarchy of cost models. Every APM can be associated with one or more cost models, reflecting the possibility that the APM could be realized on different machines. The cost models are related to each other, following the connections in the APM hierarchy. Each cost model gives the cost of every ParOp within an APM. There are several reasonable ways to assign a cost to a parallel operation: it could be inferred from the internal structure (using the organization into sites, communications and data dependencies); it could be obtained by transforming mathematically the cost of the corresponding operation in a related APM; it could be determined by measuring the real cost for a specific implementation.

The goal is to support the transformation of an algorithm from one APM to another which gives automatically the new costs. Such a cost transformation could be used in several ways. The costs could guide the transformation of an algorithm through the APM hierarchy, from an abstract specification to a concrete realization. If the costs for an APM were obtained by measuring performance of a real machine, then realistic cost transformations are possible although the transformation takes place at an abstract level. In some algorithm derivations, it is helpful to begin with a horizontal transformation within the same APM that increases the costs. This can happen because the reorganized algorithm may satisfy the constraints required to allow a vertical transformation to a more efficient algorithm using a different APM. In such complex program derivations it is helpful to be explicit about the costs and programming models in use at each stage; that is the purpose of the APM methodology.

The rest of the paper is organized as follows: Section 2 gives an overview of the APM approach. Section 3 introduces cost hierarchies to APM hierarchies. Sections 4 and 5 illustrate the approach by examples. Section 6 concludes.

#### 2 Overview of APMs

Abstract Parallel Machines (APMs) have been proposed in [14] as a formal framework for the derivation of parallel algorithms using a sequence of transfor-

mation steps. The formulation of a parallel algorithm depends not only on the algorithmic-specific potential parallelism but also on the parallel programming model and the target machine to be used. Every programming model provides a specific way to exploit or express parallelism, such as data parallel models or thread parallelism, in which the algorithm has to be described. An APM describes the behavior of a parallel programming model by providing operations (or patterns of operations) to be used in a program performed in that programming model. The basic operations provided by an APM are parallel operations (ParOps) which are combined by an APM-specific coordination language (usually, e.g., including a composition function). The application is formulated for an APM with ParOps as the smallest indivisible parallel units to express a specific application algorithm. Depending on the level of abstraction, an executable program (e.g., an MPI program for distributed memory machines) or a more abstract specification (e.g., a PRAM program for a theoretical analysis) results. The APM approach comprises:

- the specification framework of ParOps defining the smallest units in a specific parallel programming model, see Section 2.1;

- APM definitions consisting of a set of ParOps and a coordination language using them, see Section 4 for an example;

- a hierarchy of APMs built up from different APMs (expressing different parallel programming models) and relations of expressiveness between them;

- the formulation of an algorithm within one specific APM, see also Section 4 for an example; and

- the transformation of an algorithm into an equivalent algorithm (e.g., an algorithm with the same result semantics), but expressed in a different way within the same APM (horizontal transformation) or in a different APM (vertical transformation), see Section 2.3.

In the following subsections, we describe the APM framework in more detail.

#### 2.1 Framework to Define a Parallel Operation ParOp

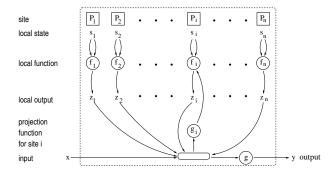

A parallel operation ParOp is executed on a number of sites  $P_1, \ldots, P_n$  (these may be virtual processors or real processors). The framework for describing a ParOp uses a local function  $f_i$  executed on site  $P_i$  using the local state  $s_i$  of  $P_i$  for  $i=1,\ldots,n$  and data provided by other sites  $z_1,\ldots,z_n$  or input data  $x_1,\ldots,x_r$ . Data from other sites used by  $P_i$  are provided by a projection function  $g_i$  which selects data from the set V of available values, consisting of the inputs  $x_1,\ldots,x_r$  and the data  $z_1,\ldots,z_n$  of all other sites, see Figure 1. The result of a ParOp is a new state  $s'_1,\ldots,s'_n$  and output data  $y_1,\ldots,y_r$ . A ParOp is formally defined by

ParOp

$$ARG(s_1, ..., s_n)$$

$(x_1, ..., x_r) = ((s'_1, ..., s'_n), (y_1, ..., y_t))$

where  $(s'_i, z_i) = f_i(s_i, g_i(V))$

$(y_1, ..., y_t) = g(V)$

$V = ((x_1, ..., x_r), z_1, ..., z_n)$

(1)

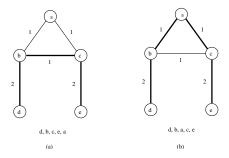

**Fig. 1.** Illustration of the possible data flow of a ParOp.  $f_i$  denotes the local computation of site  $P_i$ .  $g_i$  chooses values from  $x, A_1, \ldots, A_n$ . Only one projection function  $g_i$  is depicted so as to keep the illustration readable. The arrows do not indicate a cycle of data dependencies since the value provided by  $f_i$  need not be given back by  $g_i$ .

where ARG is a list of functions from  $\{f_1, \ldots, f_n, g_0, g_1, \ldots, g_n\}$  and contains exactly those functions that are not fully defined within the body of the ParOp. The functions  $f_1, \ldots, f_n, g_0, g_1, \ldots, g_n$  in the body of the ParOp definition can

- be defined as closed functions, so that the behavior of the ParOp is fully defined,

- define a class of functions, so that details have to be provided when using the ParOp in a program, or

- be left undefined, so that the entire function has to be provided when using the ParOp.

The functions that have to be provided when using the ParOp appear in the function argument list ARG as formal parameters in the definition (1) and as actual functions in a call of a ParOp.

The framework describes what a ParOp does, but not necessarily how it is implemented. In particular, the  $g_i$  functions imply data dependencies among the sites; these dependencies constrain the set of possible execution orders, but they may not fully define the order in an implementation. Consequently, the cost model for a ParOp may make additional assumptions about the execution order (for example, the degree of parallelism).

#### 2.2 Using APMs in a Program

To express an application algorithm, the parallel operations defined for a specific APM are used and combined according to the coordination language. When using a ParOp in a program, one does not insert an entire ParOp definition. Instead, the operation is called along with any specific function arguments that are required. Whether function arguments are required depends on the definition of the specific ParOp.

If the function arguments  $f_i$ ,  $g_i$ , are fully defined as functions in closed form, then no additional information is needed and the ParOp is called by just using its name. If one or more functions of  $f_i$ ,  $g_i$ , i = 1, ..., n, are left undefined, then the call of this ParOp has to include the specific functions possibly restricted according to the class of functions allowed. A call of a ParOp has the form

ParOp

$$ARG$$

where ARG contains exactly those functions of  $(f_1, \ldots, f_n)(g_0, \ldots, g_n)$  that are needed. This might be given in the form

$$f_{\kappa_1} = definition, \ldots, f_{\kappa_l} = definition,$$

$g_{\mu_1} = definition, \ldots, g_{\mu_k} = definition,$

$\mathsf{ParOp}(f_{\kappa_1}, ... f_{\kappa_l}, g_{\mu_1}, ... g_{\mu_k})$

#### 2.3 Vertical and Horizontal Transformations between APMs

One goal of the APM approach is to model different parallel programming models within the same framework so that the relationship between two different models can be expressed. The relationship between two parallel programming models is based on the expressiveness of the APMs which is captured in the ParOps and the coordination language combining the ParOps.

We define a relation between two different APMs in terms of a transformation mapping any program for an APM  $M_1$  onto a program for an APM  $M_2$ . The transformation is built up according to the structure of an APM program; thus it is defined on the ParOps of APM  $M_1$  and then generalized to the entire coordination language. The transformation of a ParOp is based on its result semantics, i.e., the local data and output produced from input data at a given local state.

An APM  $M_1$  can be simulated by another APM  $M_2$  if for every ParOp F of  $M_1$  there is ParOp G (or a sequence of ParOps  $G_1, \ldots, G_l$ ) which have the same result semantics as F, i.e., starting with the same local states  $s_1, \ldots, s_n$  and input data x it produces the same new local states  $s'_1, \ldots, s'_n$  and output data y.

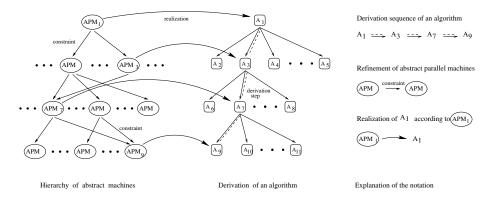

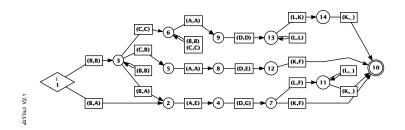

If an APM  $M_1$  can be simulated by an APM  $M_2$ , this does not necessarily mean that  $M_2$  can be simulated by  $M_1$ . If  $M_1$  can be simulated by  $M_2$ , then  $M_1$  is usually more abstract than  $M_2$ . Therefore, we arrange  $M_1$  and  $M_2$  in a hierarchical relationship with  $M_1$  being the parent node of  $M_2$ . Considering an entire set of APMs, we get a tree or a forest showing a hierarchy of APMs and the relationship between them, see Figure 2.

The relationship between APMs serves as a basis for transforming an algorithm expressed on one APM to the same algorithm now expressed in the second related APM. For two related APMs  $M_1$  and  $M_2$  a transformation operation  $T_{M_1}^{M_2}$  from  $M_1$  to  $M_2$  is defined according to the simulation relation, i.e., for each ParOp F of APM  $M_1$

$$T_{M_1}^{M_2}(F) = G$$

(or  $T_{M_1}^{M_2}(F) = G_1, \dots, G_l$ )

Fig. 2. Illustration of a hierarchy of abstract parallel machines and a derivation of an algorithm according to the hierarchy.

where G is the ParOp of  $M_2$  to which F is related. In this kind of transformation step (which is called a *vertical* transformation), the program  $A_1$  is left essentially unchanged, but it is realized on a different APM: thus  $(A_1, M_1)$  is transformed to  $(A'_1, M_2)$ . The operations  $F^j$  in  $A_1$  are replaced by the transformation  $T_{M_1}^{M_2}(F^j)$ , so that  $A_2$  uses the parallel operations in  $M_2$  which realize the operations used by  $A_1$ .

There can also be a second kind of transformation (called a *horizontal* transformation) that takes place entirely within one APM  $M_1$ :  $(A_1, M_1)$  is transformed into  $(A_2, M_1)$ , where a correctness-preserving transformation must be used to convert  $A_1$  into  $A_2$ . In the context of our methodology, this means that a proof is required that for all possible inputs  $X^0, \ldots, X^{\kappa}$  and states  $\sigma$ , the two versions of the algorithm must produce the same result, i.e.

$$A_1(X^0, \dots, X^{\kappa}, \sigma) = A_2(X^0, \dots, X^{\kappa}, \sigma).$$

There are several approaches for developing parallel programs by performing transformation steps, many of which have been pursued in a functional programming environment. Transformations based on the notion of homomorphism and the Bird-Meertens formalism are used in [10]. P3L uses a set of algorithmic skeletons like pipelines and worker farms to capture common parallel programming paradigms [3]. A parallel functional skeleton technique that emphasizes the data organization and redistributions is described in [16]. A sophisticated approach for the cost modeling of the composition of skeletons for a homomorphic skeleton system equipped with a equational transformation system is outlined in [20, 21]. The costs of the skeletons are required to be monotonic in the costs of the argument functions. The method performs a stepwise application of rewriting rules such that each application of a rewriting rule is cost-reducing. All these approaches restrict the algorithm to a single programming model, and they use the costs only to help select horizontal transformations. Vertical transformations between different programming models which could be used for the concretization of parallel programs are not supported.

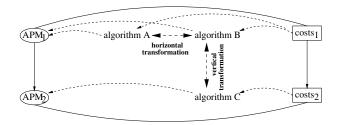

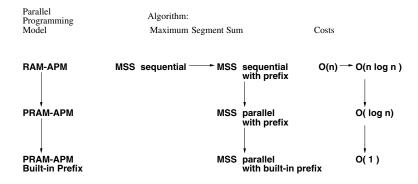

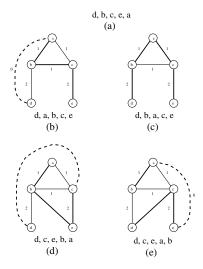

**Fig. 3.** Illustration of the connection between APMs, their corresponding costs and algorithms expressed using those APMs. The hierarchy contains only APM $_1$  and APM $_2$  with associated cost model costs $_1$  and costs $_2$ . An algorithm A can be expressed within APM $_1$  and is transformed horizontally into algorithm B within the same APM which is then transformed vertically into algorithm C within APM $_2$ .

#### 3 Cost Hierarchies

The APM method proposed in [14] has separated the specifics of a parallel programming model from the properties of an algorithm to be expressed in the model. Since the APMs and the algorithm are expressed with a similar formalism, and the relations between APMs are specified precisely, it is possible to perform program transformations between different parallel programming models. In this section, we enrich the APM approach with a third component to capture costs, see Figure 3. The goal is to provide information that supports cost-driven transformations.

#### 3.1 Cost Models for Leaf Machines

We consider an APM hierarchy whose leaves describe real machines with a programming interface for non-local operations. These would include, for example, a communication library for distributed memory machines (DMMs) or a coordination library for accessing the global memory of shared memory machines (SMMs) concurrently. Each operation of the real parallel machine is modeled by an operation of the corresponding leaf APM. By measuring the runtimes of the operations on the real parallel machine, the APM operations can be assigned costs that can be used to describe costs of a program. Since the execution times of many operations of the real machine depend on a number of parameters, the costs of the APM operations are described by parameterized runtime functions. For example, the costs of a broadcast operation on a DMM depend on the number p of participating processors and the size p of the message to be broadcast. Correspondingly, the costs are described by a function

$$t_{broad}(p,n) = f(p,n)$$

where f depends on the specific parallel machine and the communication library.

Usually, it is difficult to describe exactly the execution time of operations on real parallel machines. The local execution times are difficult to describe, since the processors may have a complicated internal architecture including a memory hierarchy, several functional units, and pipelines with different stages. Moreover techniques like branch prediction and out-of-order-execution may be used. The global execution times may be difficult to describe, since, for example, a distributed shared memory machine uses a physically distributed memory and emulates a shared memory by several caches, using, e.g., a directory-based cache coherence protocol. But for many (regular) applications and many DMMs, it is possible to describe the execution times of the machines accurately enough to compare different execution schemes for the same algorithm [23, 9]. The main concern of this article is not so much to give an accurate model for a specific (class of) parallel machines, but rather to extend an existing model so that it can be used at a higher programming level to compare different implementations of the same algorithm or to guide program transformations that lead to a more efficient program.

#### 3.2 Bottom-Up Construction of a Cost Hierarchy

Based on the cost models for the leaves of an APM hierarchy, cost models for the inner nodes of an APM hierarchy can be derived step by step. We consider an APM  $M_1$  which is the parent of an APM  $M_2$  for which a cost measure  $C_2$  has already been defined. At the beginning of the derivation  $M_2$  has to be a leaf. Since  $M_1$  is the parent of  $M_2$ , there is a transformation  $T_{M_1}^{M_2}$  which assigns each parallel operation F of  $M_1$  an equivalent sequence  $G_1, \ldots, G_l$  of parallel operations, each of which has assigned a cost  $C_2(G_i)$ . We define a cost measure  $C_{M_1 \leftarrow M_2}$  based on the cost measure  $C_2$  for  $M_2$  by

$$C_{M_1 \leftarrow M_2}(F) = \sum_{i=1}^{l} C_2(G_i).$$

(2)

A cost measure  $C_2$  for  $M_2$  may again be based on other cost measures, if  $M_2$  is not a leaf. If the programmer intends to derive a parallel program for a real parallel machine R which is a leaf in the APM hierarchy, each intermediate level APM is assigned a cost measure that is based on the cost of R, i.e., the selection of the cost measure is determined by the target machine. Thus, for each path from a leaf to an inner node B there is a possibly different cost measure.

We now can define the equivalence of cost measures for an inner node M of an APM hierarchy with children  $M_1$  and  $M_2$ . Cost measures  $C_{M \leftarrow M_1}$  and  $C_{M \leftarrow M_2}$  for APM M can be defined based on cost measures for  $C_1$  and  $C_2$  of  $M_1$  and  $M_2$ , respectively. We call  $C_{M \leftarrow M_1}$  and  $C_{M \leftarrow M_2}$  equivalent if for arbitrary programs  $A_1$  and  $A_2$ , the following is true:

If

$$C_{M \leftarrow M_2}(A_1) \le C_{M \leftarrow M_2}(A_2)$$

then  $C_{M \leftarrow M_1}(A_1) \le C_{M \leftarrow M_1}(A_2)$

and vice versa. If two cost measures are equivalent, then both measures can be used to derive efficient programs and it is guaranteed that both result in the

same program since both have the same notion of optimality. Note that the equivalence of two cost measures for an APM does not require that they yield the same cost value for each program.

#### 3.3 Monotonicity of Cost Measures

The cost measure for an APM can be used to guide horizontal transformations. For this purpose, a cost measure must fulfil the property that a horizontal transformation that is useful for an APM M is also useful for all concretizations of M. This property is described more precisely by the notion of monotonicity of cost measures. We consider APMs  $M_2$  and  $M_1$  where  $M_2$  is a child of  $M_1$  in the APM hierarchy. Let  $A_1$  and  $A_2$  be two programs for APM  $M_1$  where  $A_2$  is obtained from  $A_1$  by a horizontal transformation  $T_{M_1}$  which reduces the costs according to a cost measure  $C_1$ , i.e.,

$$C_1(A_1) \ge C_1(A_2) = C_1(T_{M_1}(A_1)).$$

Let  $T_{M_1}^{M_2}$  be the vertical transformation from  $M_1$  to  $M_2$ , i.e., the corresponding programs to  $A_1$  and  $A_2$  on APM  $M_2$  are  $A_1' = T_{M_1}^{M_2}(A_1)$  and  $A_2' = T_{M_1}^{M_2}(A_2)$  respectively. Both these programs can be assigned costs according to a cost measure  $C_2$  of APM  $M_2$ . The cost measures  $C_1$  and  $C_2$  are consistent only if the increase in efficiency that has been obtained by the transformation from  $A_1$  to  $A_2$  carries over to APM  $M_2$ , i.e., only if

$$C_2(T_{M_1}^{M_2}(A_1)) \ge C_2(T_{M_1}^{M_2}(A_2)).$$

This property is captured by the following definition of monotonicity. The transformation  $T_{M_1}^{M_2}$  is monotonic with respect to the costs  $C_1$  and  $C_2$ , if for arbitrary programs  $A_1$  and  $A_2$

$$C_1(A_1) \ge C_1(A_2)$$

implies  $C_2(T_{M_1}^{M_2}(A_1)) \ge C_2(T_{M_1}^{M_2}(A_2))$ .

The bottom-up construction of cost measures according to an APM hierarchy creates monotonic cost measures; this can be proven by a bottom-up induction over the APM tree using definition (2) of cost measures. In the next section, we describe the PRAM model with different operation sets in the APM methodology. For this example, we do not use the bottom-up cost definition but use the standard costs of the PRAM model.

#### 3.4 Other Cost Models

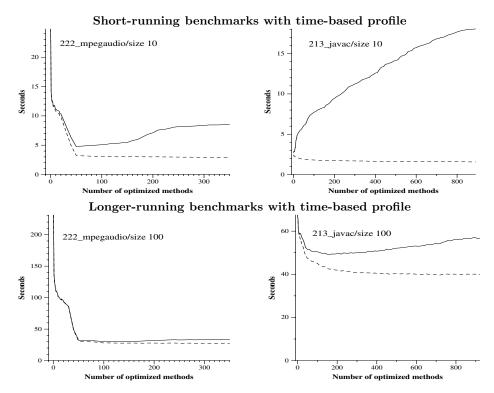

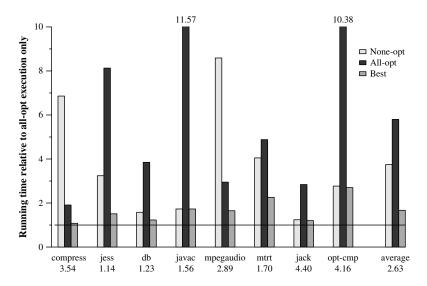

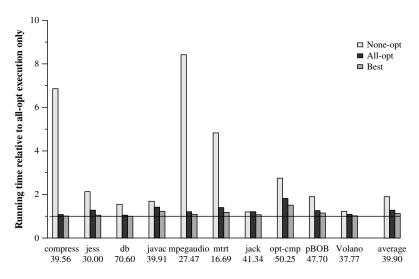

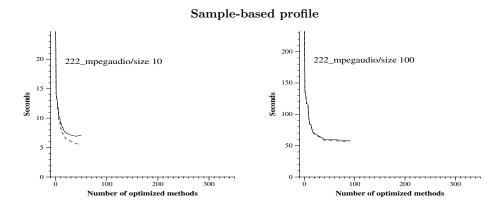

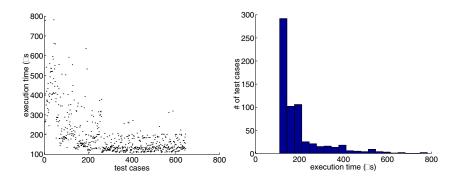

One of the most popular parallel cost models is the PRAM model [8] and its extensions. Because none of the PRAM models was completely satisfactory, a number of other models have been proposed that are not based on the existence of a global memory, including BSP [22] and logP [6]. Both provide a cost calculus by modeling the target architecture with several parameters that capture its computation and communication performance. The supersteps in the BSP model